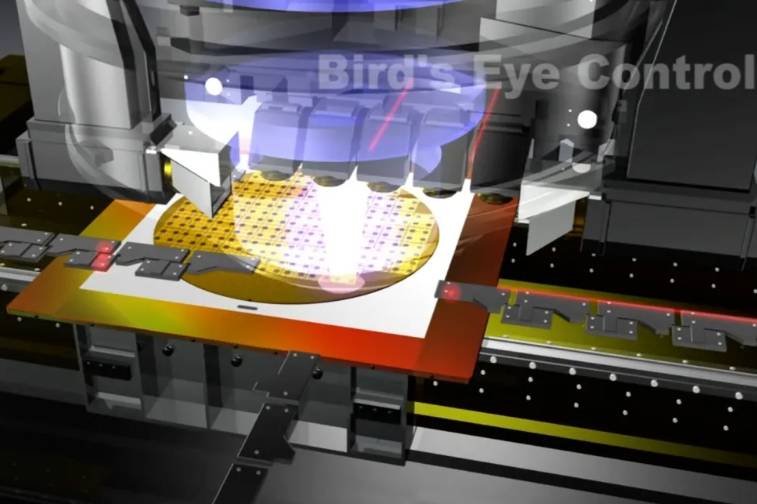

在當(dāng)今這個科技日新月異的時代,芯片無疑扮演著舉足輕重的角色,它不僅構(gòu)成了算力、數(shù)字化和信息化的基石,更在某種程度上預(yù)示著經(jīng)濟(jì)的繁榮與否。可以說,算力與經(jīng)濟(jì)緊密相連,算力不強(qiáng),經(jīng)濟(jì)發(fā)展亦難以如意。

近年來,芯片行業(yè)無疑是全球發(fā)展最為迅猛的領(lǐng)域之一。從芯片工藝的飛速進(jìn)步便可見一斑:從10nm到7nm,再到5nm、3nm,乃至如今正邁向2nm的征程,每一步都見證了技術(shù)的巨大飛躍。ASML甚至預(yù)言,到2037年,我們或?qū)⒁娮C0.2nm芯片的誕生。從2025年至2037年,每一年都將見證新的突破,推動芯片行業(yè)不斷向前。

然而,盡管芯片工藝不斷精進(jìn),芯片行業(yè)卻面臨著兩大嚴(yán)峻挑戰(zhàn)。首先,芯片制造的良率問題日益凸顯。以三星的3nm工藝為例,據(jù)傳其良率僅為20%左右,這意味著每生產(chǎn)10顆芯片,就有8顆可能存在問題。這一狀況迫使高通、英偉達(dá)等企業(yè)轉(zhuǎn)而尋求臺積電的代工服務(wù)。事實(shí)上,隨著工藝的不斷進(jìn)步,對設(shè)備、技術(shù)和材料的要求愈發(fā)嚴(yán)苛,良率下降已成為不可避免的趨勢。未來,隨著工藝的持續(xù)精進(jìn),良率可能會進(jìn)一步降低,曾經(jīng)被視為標(biāo)準(zhǔn)的85%良率,或許將被60%或70%所取代。良率的低下將直接導(dǎo)致成本的急劇上升。

第二大難題則在于流片成功率的持續(xù)下滑。據(jù)西門子提供的數(shù)據(jù),以往芯片行業(yè)的正常流片首次成功率約為30%,但近年來這一數(shù)字持續(xù)下跌,至2024年已降至24%。而到了2025年,更是預(yù)計(jì)將降至14%。這意味著,在100家嘗試流片的芯片企業(yè)中,僅有14家可能成功,其余86家則將面臨失敗。流片成功率的下降,一方面與工藝的復(fù)雜性增加有關(guān),另一方面則與芯片結(jié)構(gòu)的日益復(fù)雜密不可分。如今的芯片融合了多種架構(gòu)、類型和技術(shù),這無疑增加了流片的難度。與以往相比,芯片的迭代速度也大大加快,從過去的平均18個月縮短至如今的不到12個月。時間的緊迫性增加了出錯的風(fēng)險,從而降低了流片的成功率。

更為嚴(yán)峻的是,流片成功率的下降并非孤立現(xiàn)象。它與芯片制造的良率問題相互交織,共同構(gòu)成了芯片行業(yè)面臨的巨大挑戰(zhàn)。一方面,良率的低下導(dǎo)致成本上升,增加了企業(yè)的財(cái)務(wù)壓力;另一方面,流片成功率的下滑則意味著更多的研發(fā)時間和資源將被浪費(fèi),進(jìn)一步拖慢了芯片行業(yè)的發(fā)展步伐。

面對這些挑戰(zhàn),芯片行業(yè)必須尋求新的突破點(diǎn)。一方面,需要不斷優(yōu)化制造工藝和設(shè)備,提高良率和流片成功率;另一方面,也需要加強(qiáng)研發(fā)創(chuàng)新,探索新的芯片結(jié)構(gòu)和材料,以應(yīng)對日益復(fù)雜的市場需求。只有這樣,才能在接近物理極限的工藝條件下,繼續(xù)推動芯片行業(yè)的蓬勃發(fā)展。