半導體封裝領域正迎來技術革新,面板級扇出封裝(FOPLP)成為行業焦點。這項由臺積電等廠商主導研發的新型封裝技術,通過將傳統晶圓載板替換為矩形面板,實現了成本與效率的雙重突破。據供應鏈消息,FOPLP設備已進入客戶測試階段,首批試產良率達90%,但大尺寸應用仍需突破量產瓶頸。

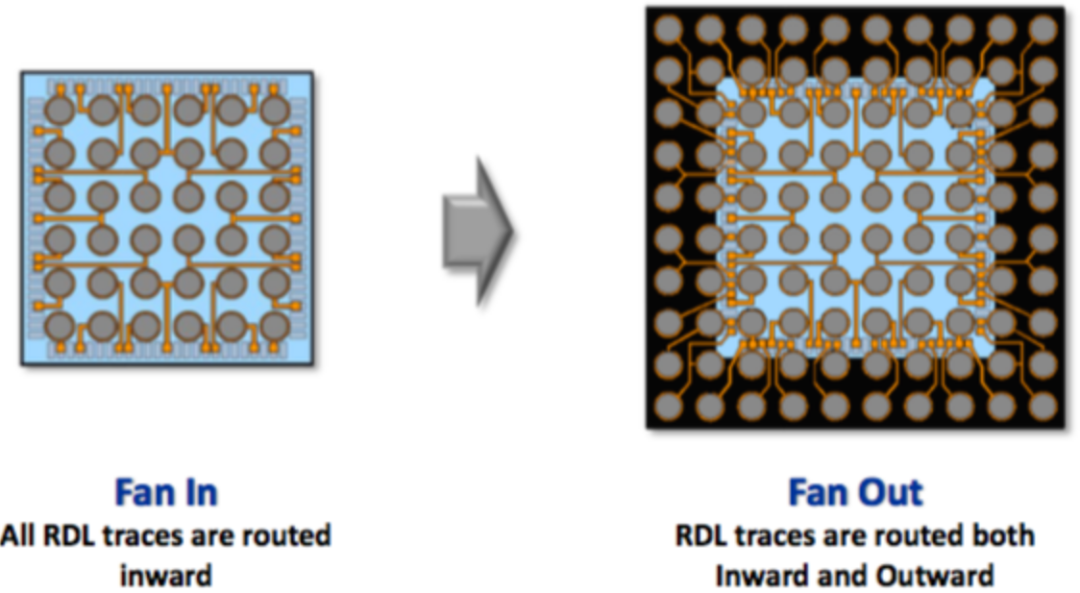

FOPLP的核心優勢在于載板形態的革新。相較于傳統晶圓級扇出封裝(FOWLP)采用的圓形載板,FOPLP使用600×600毫米的方形面板,面積超過12英寸晶圓的五倍。這種設計使材料利用率從57%提升至87%,顯著降低了單位封裝成本。技術原理上,該技術通過在芯片投影面積外圍擴展導線重新分布層(RDL),突破了扇入型封裝的空間限制。

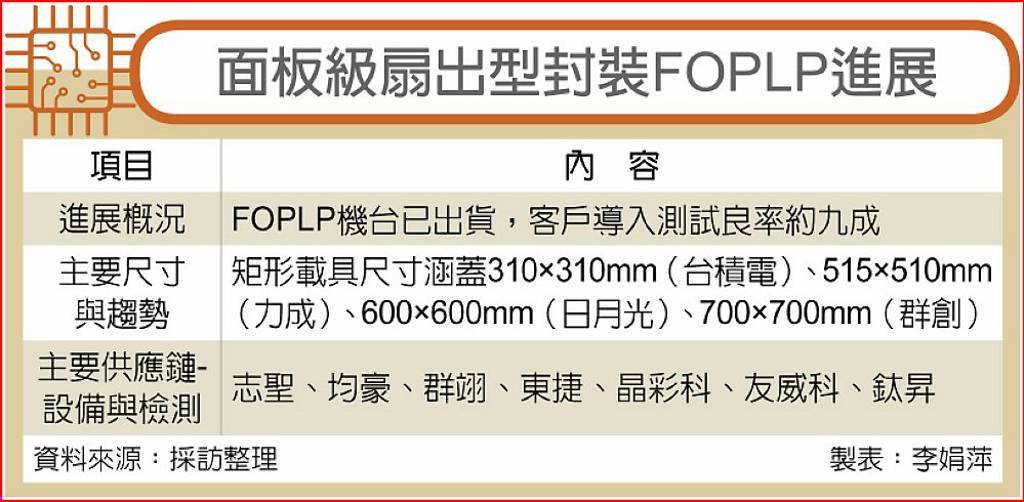

行業推進呈現雙軌并行態勢。群創光電與力成科技已實現小規模量產,主要應用于電源管理芯片等中小型器件封裝。其中力成科技部署新一代激光與點膠設備后,試產良率突破90%,預計明年可達95%以上。另一條技術路徑由臺積電主導,其開發的CoPoS(晶圓級面板封裝)方案瞄準英偉達、AMD等廠商的高性能GPU需求,目前試產階段仍面臨技術瓶頸。

載板材料與尺寸標準逐步確立。當前主流方案包括臺積電310×310毫米、力成515×510毫米、日月光600×600毫米及群創700×700毫米四種規格,材質以金屬和玻璃為主。臺積電特別投資TGV(穿玻璃通孔)技術推動玻璃基板發展,其專屬研發團隊已建立完整產線,原定2027年的量產計劃可能提前實施。

產能調整伴隨技術升級同步進行。臺積電今年8月宣布將在兩年內淘汰6英寸晶圓產線,并整合8英寸產能。晶圓二廠(6英寸)與五廠(8英寸)的改造方向尚未確定,但業界猜測可能轉型為CoPoS專用產線。這一系列布局顯示,先進封裝技術正成為半導體廠商競爭的新戰場。